#### **Computer Organization & Assembly Language Programming**

|                                                        | Memory                                         |

|--------------------------------------------------------|------------------------------------------------|

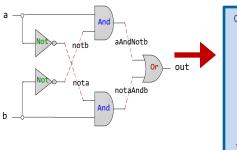

| CHIP Xor {                                             | program                                        |

| IN a, b;<br>OUT out;<br>PARTS:<br>Not(in=a, out=nota); | data                                           |

| Not(in=b, out=notb);<br>And(a=nota, b=b, out=w1);      | Memory<br>address<br>input<br>instruction data |

| And(a=a, b=notb, out=w2);<br>Or(a=w1, b=w2, out=out);  | address address C                              |

| }                                                      |                                                |

#### **Lecture # 11**

## **Design of Registers**

Slides of first half of the course are adapted from: <u>https://www.nand2tetris.org</u> Download s/w tools required for first half of the course from the following link: https://drive.google.com/file/d/0B9c0BdDJz6XpZUh3X2dPR1o0MUE/view

1110001100001000

## **Today's Agenda**

- Review of Sequential Chips

- What are Registers

- Design of 1-bit Register

- HDL for 1-bit Register

- Design of 16-bit Register

- HDL for 16-bit Register

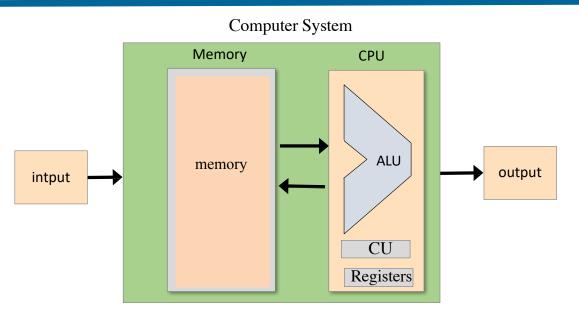

# **Review of Sequential Chips**

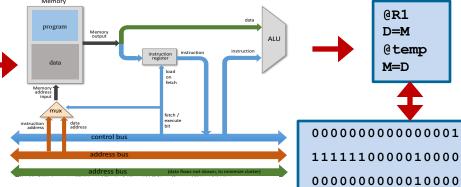

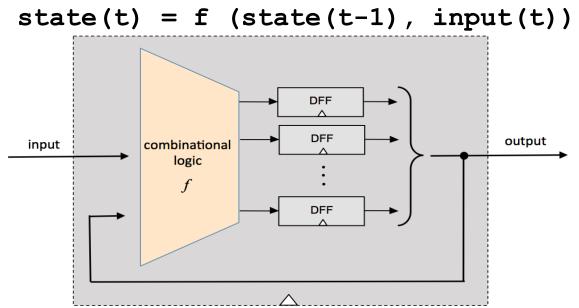

- Sequential chips are capable of maintaining state, and, optionally acting on the state, and on the current input

- The simplest and most elementary sequential chip is DFF, which maintain a state, i.e., the value of the input from the previous time unit

- Using DFF we can design registers, and using registers we can design RAM, whose state is the current values of all its registers. Given an address, the RAM emits the value of the selected register

- All combinational chips are constructed from NAND gates, while all sequential chips are constructed from DFF gates, and combinational chips

# **CPU Registers**

#### **CPU Registers**

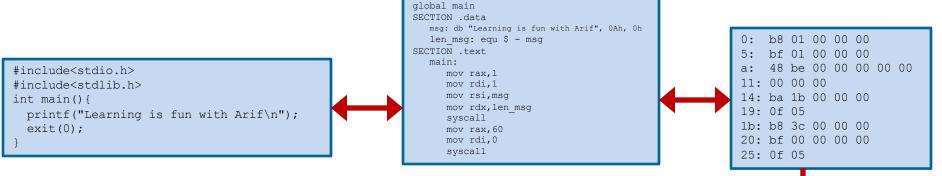

- A register is a small memory place inside the CPU that may hold data, memory address or instruction

- The size of registers in a 64-bit computer must be of 64 bits

- In our Hack computer is a 16 bit computer, so the registers we are going to design will be of 16 bits

- There are several different classes of CPU registers which works in coordination with the computer memory to run operations efficiently. (More on it later)

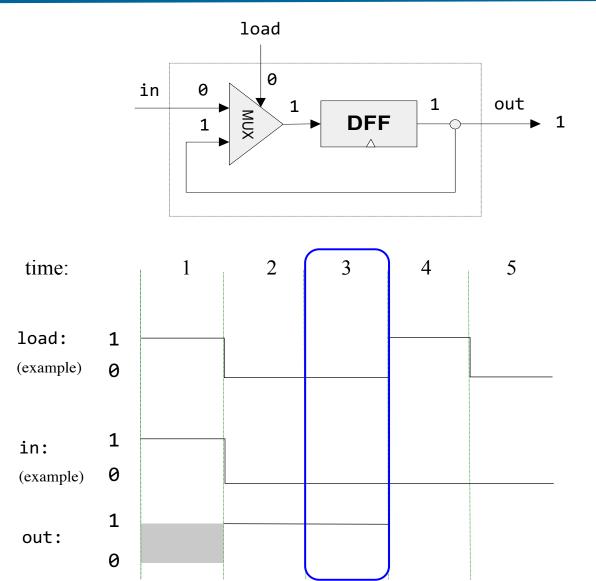

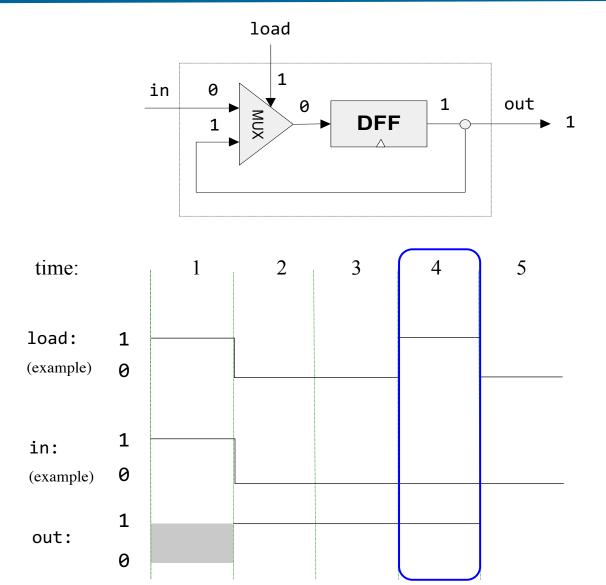

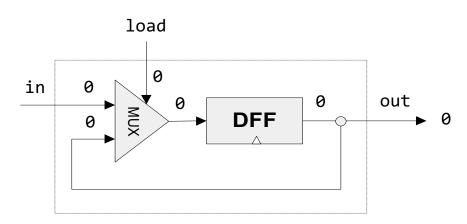

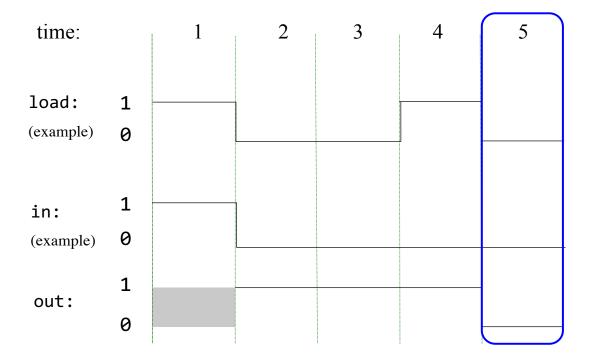

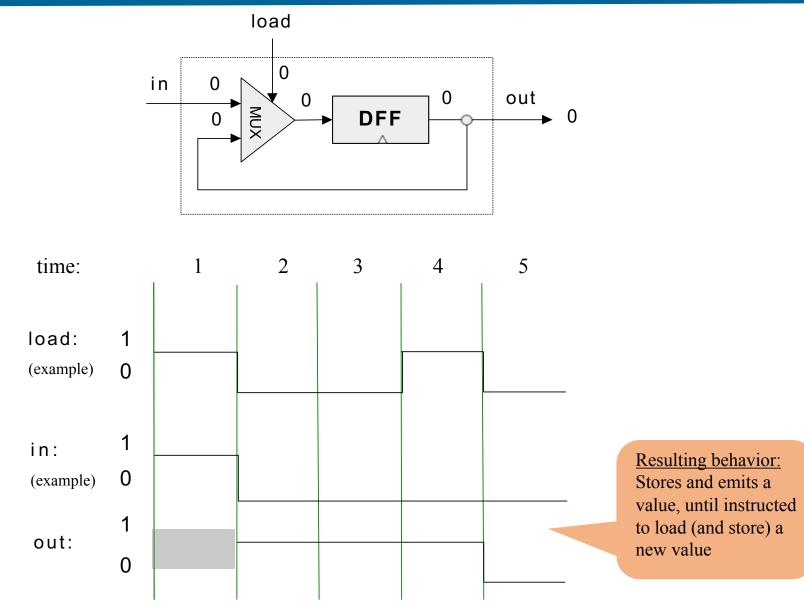

# **1-Bit Register**

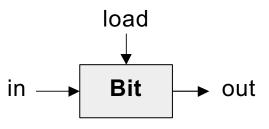

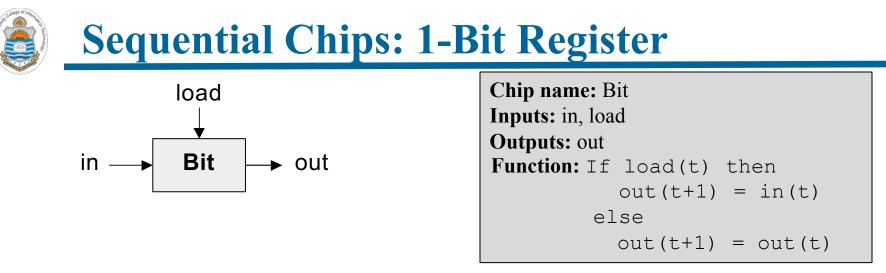

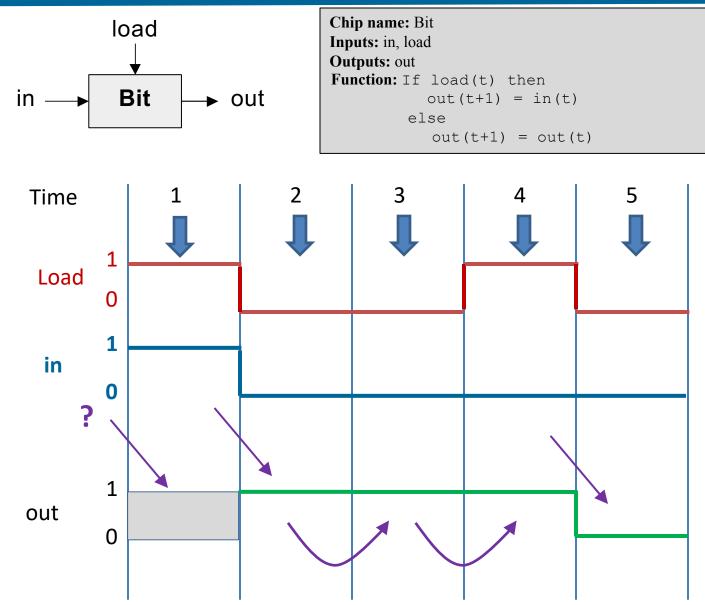

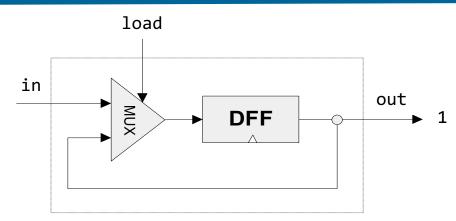

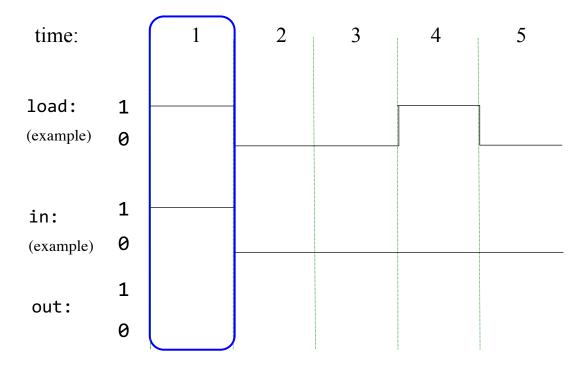

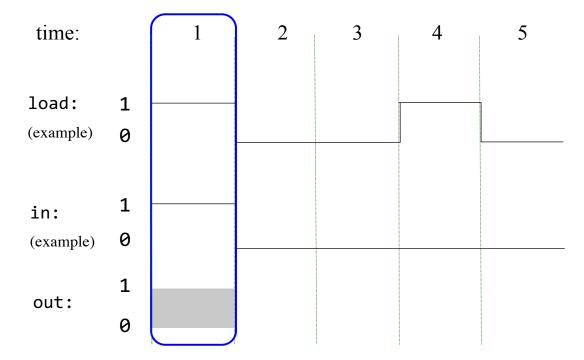

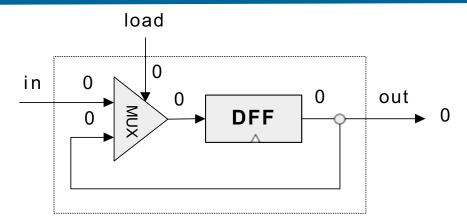

- A single-bit register, which we call Bit, or binary cell, is designed to store a single bit of information (0 or 1)

- The chip interface diagram shows that it has two input pins and one output pin. The input pin carries a data bit, the load pin enables the cell for writes, and an output pin that emits the current state of the cell

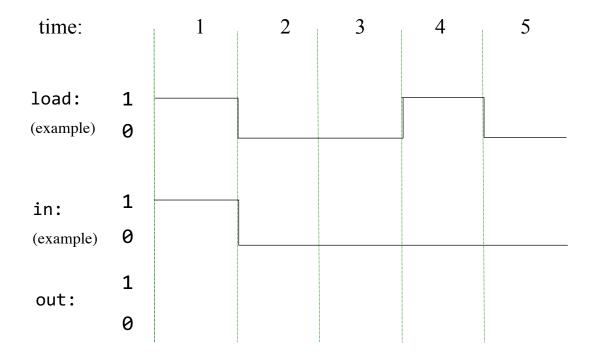

- When you read the out pin of the binary cell, you will always get whatever is the state of the binary cell

- To write the binary cell, we set the load bit to 1, now what ever is there on the input bit will be stored inside the binary cell and will be available on the out pin in the next clock cycle

- When the load bit is zero, the chip keep remembering the last input that was loaded into it for infinity until a new load operation is performed

- Goal: Remember an input bit forever, until requested to load a new value

- More accurately:

- Stores a bit until...

- Instructed to load, and store, another bit

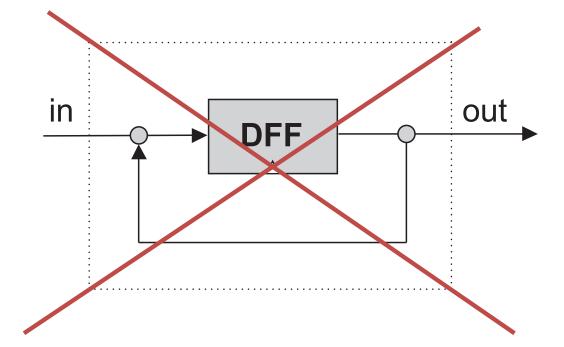

## **Sequential Chips: 1-Bit Register**

# And a series of the series of

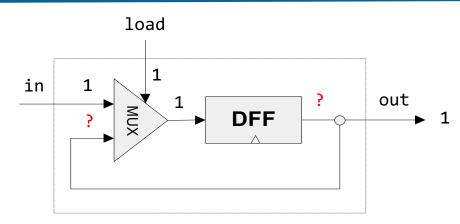

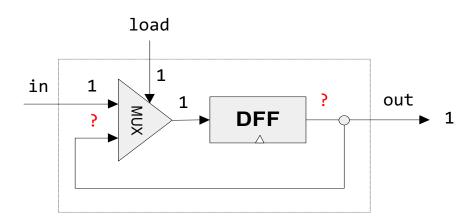

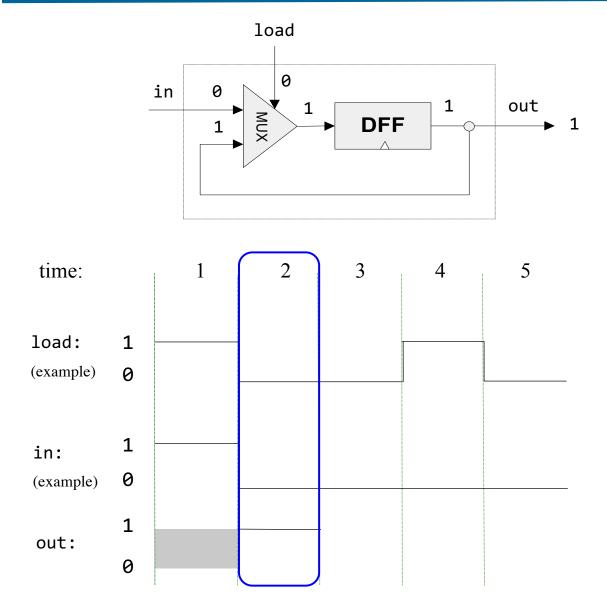

## **1-Bit Register Implementation**

### **Computers Are Flexible**

## HDL for 1-bit Register

#### Bit.hdl

```

/** 1-bit register:

* If load[t] == 1 then. //load input in the ff

* out[t+1] = in[t]

* else //out does not change

*/ (out[t+1] = out[t])

CHIP Bit {

IN in, load;

OUT out;

PARTS:

Mux(a=sendBack, b=in, sel=load, out=MuxOut);

DFF(in=MuxOut, out=sendBack, out=out);

```

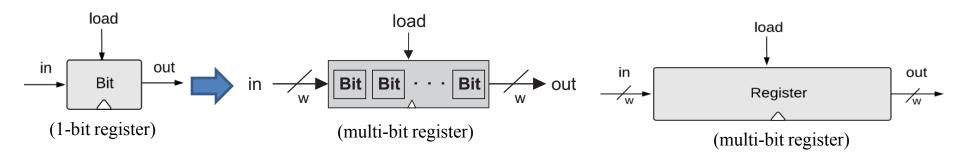

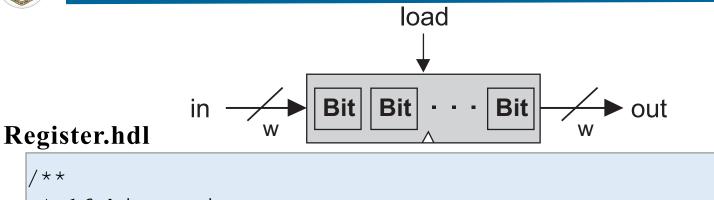

## **Multi-Bit Register**

## **Multi-Bit Register**

- A register is actually a group of flip-flops, each flip flop capable of storing one bit of information

- An n-bit register consists of a group of n flip-flops capable of storing n bits of binary information. In this course we will focus on designing of 16-bit registers for our computer

- A 16 bit register can be created from an array of 16 1-bit registers

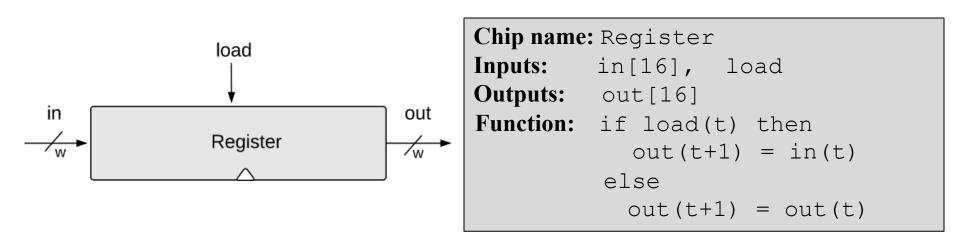

## **16 Bit Register API**

- The API of the 16 bit Register chip is essentially the same as the 1-bit register, except that the input and output pins are designed to handle multi-bit values

- The interface diagram and API of a 16-bit register is shown below

- The Bit and Register chips have exactly the same read/write behavior:

- **Read:** To read the contents of a register, we simply probe its output

- Write: To write a new data value **d** into a register, we put **d** in the **in** input and set the load input to 1. In the next clock cycle, the register commits to the new data value, and its output starts emitting **d**, and it will keep emitting this new value forever till the time we decide to write a new value in it

## HDL for 16-bit Register

```

* 16-bit register:

* If load[t] == 1 then out[t+1] = in[t]

* else out does not change CHIP Bit (

IN in, load;

*/

OUT out;

CHIP Register {

PARTS:

Mux(a=sendBack, b=in, sel=load, out=MuxOut);

IN in[16], load;

DFF(in=MuxOut, out=sendBack, out=out);

OUT out[16];

PARTS:

Bit(in=in[0], load=load, out=out[0]);

Bit(in=in[1], load=load, out=out[1]);

Bit(in=in[2], load=load, out=out[2]);

Bit(in=in[3], load=load, out=out[3]);

Bit(in=in[15], load=load, out=out[15]);

```

## **Things To Do**

• Practice writing HDL of the register chips and verify their behavior by loading and running them on the h/w ssimulator. You can download the .hdl, .tst and .cmp files of above chips from the course bitbucket repository:

https://bitbucket.org/arifpucit/coal-repo/

• Practice the different timing diagrams that we have used to describe the behavior of D-flip flop and the single bit register on a piece of paper by yourself.

#### Coming to office hours does NOT mean you are academically week!

O.k., and now you'll do exactly what I'm telling you !

Access